- 您现在的位置:买卖IC网 > Sheet目录3832 > AT87C52X2-3CSUM (Atmel)IC 8051 MCU 8K OTP 40MHZ 40DIP

29

TS8xCx2X2

4184I–8051–02/08

Power-off Flag

The power-off flag allows the user to distinguish between a “cold start” reset and a

“warm start” reset.

A cold start reset is the one induced by VCC switch-on. A warm start reset occurs while

VCC is still applied to the device and could be generated for example by an exit from

power-down.

The power-off flag (POF) is located in PCON register (See Table 17.). POF is set by

hardware when VCC rises from 0 to its nominal voltage. The POF can be set or cleared

by software allowing the user to determine the type of reset.

The POF value is only relevant with a Vcc range from 4.5V to 5.5V. For lower Vcc value,

reading POF bit will return indeterminate value.

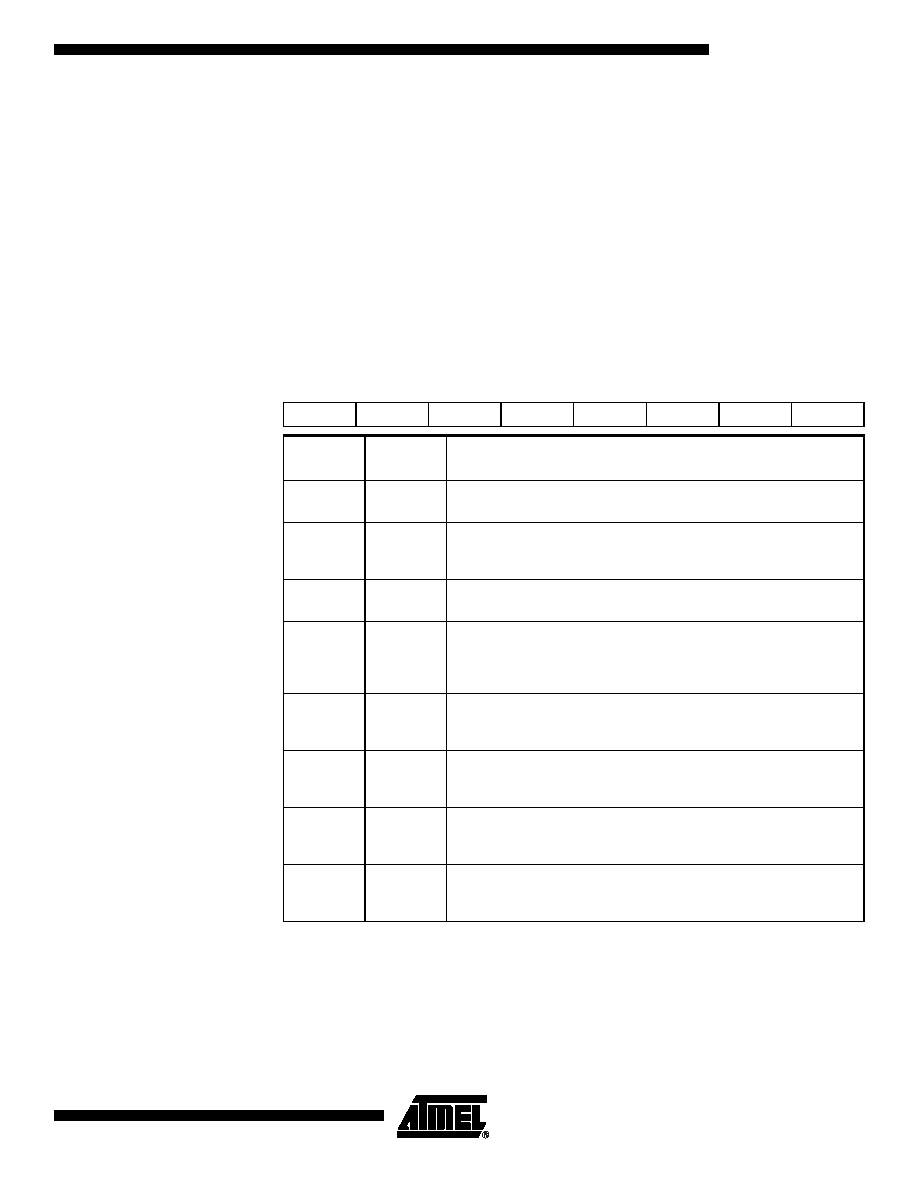

Table 17. PCON Register

PCON - Power Control Register (87h)

Reset Value = 00X1 0000b

Not bit addressable

7

6

5

4

3

2

1

0

SMOD1

SMOD0

-

POF

GF1

GF0

PD

IDL

Bit

Number

Bit

Mnemonic

Description

7

SMOD1

Serial port Mode bit 1

Set to select double baud rate in mode 1, 2 or 3.

6

SMOD0

Serial port Mode bit 0

Clear to select SM0 bit in SCON register.

Set to to select FE bit in SCON register.

5

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

4

POF

Power-off Flag

Clear to recognize next reset type.

Set by hardware when VCC rises from 0 to its nominal voltage. Can also be

set by software.

3

GF1

General purpose Flag

Cleared by user for general purpose usage.

Set by user for general purpose usage.

2

GF0

General purpose Flag

Cleared by user for general purpose usage.

Set by user for general purpose usage.

1

PD

Power-down mode bit

Cleared by hardware when reset occurs.

Set to enter power-down mode.

0

IDL

Idle mode bit

Clear by hardware when interrupt or reset occurs.

Set to enter idle mode.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16C924-04/L

IC MCU OTP 4KX14 LCD DVR 68PLCC

PIC16F767-I/SO

IC PIC MCU FLASH 8KX14 28SOIC

PIC24FJ64GA310-I/PF

MCU 16BIT 64KB FLASH 100TQFP

DSPIC33FJ64GP202-E/MM

IC DSPIC MCU/DSP 64K 28-QFN

PIC16F876A-I/ML

IC MCU FLASH 8KX14 A/D 28QFN

PIC16F876A-I/SO

IC MCU FLASH 8KX14 EE 28SOIC

PIC16F876A-I/SP

IC MCU FLASH 8KX14 EE 28DIP

AT87C51RD2-3CSUM

IC 8051 MCU 64K OTP 40MHZ 40DIP

相关代理商/技术参数

AT87C52X2-3CSUV

功能描述:8位微控制器 -MCU Microcontroller

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-RLRUM

功能描述:8位微控制器 -MCU 0.5um RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-RLTUL

功能描述:8位微控制器 -MCU C72X2C52 0.5m OTP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-RLTUM

功能描述:8位微控制器 -MCU C72X2 C52 0.5 m X 2 OTP 0.5 NV RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-RLTUV

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Microcontroller 8 Kbytes ROM/OTP, ROMless

AT87C52X2-SLRUL

功能描述:8位微控制器 -MCU Microcontroller RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-SLRUM

功能描述:8位微控制器 -MCU Microcontroller RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-SLSUL

功能描述:8位微控制器 -MCU OTP C52/8K 40MHZ 3V COM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT